# **Chapter 11**

# Schematic-on-Top with VHDL Tutorial

This chapter contains the following sections:

- "Introduction"

- "Required Background Knowledge"

- "Design Flow"

- "Software Installation"

- "Starting the Design Manager"

- "Copying the Tutorial Files"

- "Starting Design Architect"

- "Completing the Calc Design"

- "Using a Constraints File"

- "Performing Functional Simulation"

- "Using Pld\_men2edif"

- "Using the Xilinx Design Manager"

- "Performing Timing Simulation"

- "Examining Routed Designs with FPGA Editor"

- "Verifying the Design Using a Demonstration Board"

- "Command Summaries"

- "Further Reading"

# Introduction

This chapter guides you through a typical field-programmable gate array (FPGA) and complex programmable logic device (CPLD)

design procedure from schematic entry with instantiated HDL to completion of a functioning device. It uses a design called Calc, a 4bit processor with a stack. In the first part of the tutorial, you use the Design Architect, the Mentor Graphics design entry tool, to link HDL entities to Mentor symbols and instantiate those symbols into the Calc design. Next, you use QuickSim Pro, the Mentor Graphics schematic/HDL simulator, to perform a functional simulation on it. In the third step, you use the Xilinx Design Manager to implement the design. Finally, you verify the design's timing by using pld\_quicksim. The simple design example used in this tutorial demonstrates many system features that you can apply to more complex FPGA and CPLD designs.

**Note:** Although this tutorial describes creating and processing FPGA designs, you can apply most of the steps to CPLD designs. Unlike the "Schematic Design Tutorial", this tutorial focuses completely on FPGAs. For information on retargeting a design to a different device family, see the "Targeting the Design for the XC9000 Family" section of the "Schematic Design Tutorial".

This tutorial includes instructions on the following:

- Installing the tutorial files

- Using Mentor Graphics Design Manager

- Using Mentor Graphics Design Architect

- Completing the SEG7DEC and ALU blocks in the Calc design

- Performing functional simulation on the Calc design in QuickSim Pro

- Converting the design to an EDIF file using pld\_men2edif

- Implementing the design using pld\_dsgnmgr

- Configuring the Xilinx Design Manager/Flow Engine

- Performing timing simulation on the routed Calc design in pld\_quicksim

- Examining routed designs with the Editor for Programmable ICs (FPGA Editor)

- Verifying the Calc design on a demonstration board

- Command summaries

# **Required Background Knowledge**

**Note:** This tutorial focuses specifically on the procedures for importing VHDL modules into Design Architect schematics. Refer to the "Schematic Design Tutorial" for information on basic objectmanagement procedures in Design Manager, schematic-entry procedures in Design Architect, or Xilinx-specific concepts such as CONFIG, STARTUP, and incremental design.

This tutorial assumes that you have a basic understanding of the following:

- UNIX operating system

- Motif Windows. Mentor Graphics applications conform to the Motif window style.

- Basic knowledge of Mentor Graphics tools, such as editing MGC location maps, manipulating design objects and launching applications in Design Manager, and adding and working with design elements in Design Architect. If you are not familiar with these procedures, see the "Schematic Design Tutorial" chapter.

**Note:** When you are instructed to close a window, it is important that you exit from the window rather than iconize it.

# **Design Flow**

See the "Design Flows" section of the "Introduction" chapter for the design flow involved in using the Mentor Graphics interface. That chapter also describes the general steps for creating a top-level schematic design with instantiated VHDL modules using the Mentor interface.

**Note:** To instantiate Verilog modules into a schematic in Design Architect, you must first encapsulate them within a VHDL entity. You then encapsulate the VHDL entity into the schematic.

The tutorial design is targeted for an XC4000E device. You can use a Xilinx demonstration board to test the functionality of your design. Make sure your demonstration board and software support your selected device. To determine compatibility, refer to the release notes that came with your software package.

# **Software Installation**

### **Required Software**

The following versions of software are required to perform this tutorial:

- Mentor Graphics Version C.2, including Mentor Design Manager, Design Architect, QuickSim, QuickPath, as well as the programs needed to read and write EDIF netlists (ENRead and ENWrite), which require special licensing

- A third-party FPGA/CPLD synthesis tool, such as LeonardoSpectrum (Exemplar Logic)

- Model Technology ModelSim 5.2d

- Xilinx/Mentor Graphics Interface Version 2.1i

- Xilinx Development System Version 2.1i

### **Before Beginning the Tutorial**

Before beginning the tutorial, set up your workstation to use Mentor Graphics and Xilinx Development System software as follows:

1. Verify that your system is properly configured.

Consult the release notes that came with your software package for more information.

- 2. Install the following sets of software:

- Xilinx Development System Version 2.1i

- Xilinx/Mentor Graphics Interface Version 2.1i

- Mentor Graphics Version C.2, including Mentor Design Manger, Design Architect, QuickSim, QuickPath, as well as the programs needed to read and write EDIF netlists (ENRead and ENWrite), which require special licensing

- Model Technology ModelSim 5.2d

- A third-party FPGA/CPLD synthesis tool, such as LeonardoSpectrum (Exemplar Logic)

- 3. Verify the installation, using the "Configuring Your System" section of the "Getting Started" chapter as a guide.

4. Add a reference to \$XILINX\_TUTORIAL to your MGC\_LOCATION\_MAP file.

All of the tutorial designs use the variable \$XILINX\_TUTORIAL as part of their path references. For example, the design object alu in the \$XILINX/mentor/tutorial/calc\_sot directory uses the path reference \$XILINX\_TUTORIAL/calc\_sot/alu to define where it is located in the directory structure.

With this definition added to the location map as defined in the "Getting Started" chapter, the complete location-map file should, at a minimum, look like:

MGC\_LOCATION\_MAP\_1 (empty line) \$MGC\_GENLIB (empty line) \$LCA (empty line) \$SIMPRIMS (empty line) \$XILINX\_TUTORIAL /home/bclinton/mentor/xtutorial

This assumes the Xilinx tutorial files have been placed under /home/bclinton/mentor/xtutorial. For example, the full path to the schematic-on-top tutorial would be /home/bclinton/mentor/xtutorial/calc\_sot

Refer to the "Schematic Design Tutorial" chapter or the Mentor Graphics documentation for more information on location maps.

### Installing the Tutorial

If you have not already done so, download the tutorial files from ftp://ftp.xilinx.com/pub/documentation/M2.1i\_tutorials/ men\_tut\_files\_21i.tar.Z. Once they are downloaded un-compress and un-tar the files.

#### uncompress men\_tut\_files\_21i.tar.Z

tar xvf men\_tut\_files\_21i.tar

#### **Standard Directory Structure**

When a design object is created in Mentor Graphics, a directory is created in the project directory with the same name as the design object. This directory contains a schematic directory, symbol files, viewpoint files, and part interfaces. The directory is identified as a design object by the file, *design\_name*.mgc\_component.attr, that resides at the same level as the directory which has the name. For example, if a schematic named calc is created, a calc directory is created, and at the same level the file, calc.mgc\_component.attr, is created. The calc directory contains all the files that describe calc.

**Note:** In this tutorial, file names and directory names are in lower case and the design example is referred to as Calc.

#### **Tutorial Directory and Files**

You will complete the Calc design in this tutorial. During the tutorial installation, the /tutorial directory is created; design object directories are created; and the tutorial files needed to complete the design are copied to the calc\_sot directory. Some of the files you need to complete the tutorial design are not copied, because you create these files in the tutorial. However, solutions directories with all input and output files are provided. They are located in the /tutorial directory and are listed in the following table.

| Directory | Description                                        |  |

|-----------|----------------------------------------------------|--|

| calc_sch  | Schematic (Design Architect) tutorial directory    |  |

| calc_4ke  | Schematic solution directory for XC4003E-PC84      |  |

| calc_9k   | Schematic solution directory for XC95108-PC84      |  |

| calc_sot  | Schematic-on-top tutorial directory (uses XC4003E) |  |

Table 11-1 Tutorial Design Directories

The solution directories contain the design files for the completed tutorial, including schematics, intermediate directories, and the bitstream file. Different intermediate files are created for different device families. Do not overwrite any files in the solutions directories.

The calc\_sot directory contains the incomplete copy of the tutorial design. The installation program copies a few intermediate files to the calc\_sot tutorial directory, and you create the remaining files when you perform the tutorial. In a later step, you copy the calc\_sot direc-

tory to another area and perform the tutorial in this new area. Each design component directory has associated with it a file called *file-name*.mgc\_component.attr. This file identifies the corresponding directory as a Mentor Graphics design component.

# **Starting the Design Manager**

To start the Design Manager that is configured for Xilinx designs, type the following at the operating system command line:

#### pld\_dmgr

The Design Manager Window appears as shown in the following figure.

Figure 11-1 Mentor Design Manager Window

**Note:** This tutorial assumes you are familiar with basic Design Manager procedures. For more information on these procedures, see the "Schematic Design Tutorial".

# **Copying the Tutorial Files**

The schematic-on-top Calc tutorial files are located in the /tutorial/ calc\_sot directory. To use the Copy operation in Design Manger to copy these files to a local area, perform the following steps:

- 1. In the Navigator window, move to the directory where the tutorial files were installed.

- 2. Select the calc\_sot directory.

- 3. To see the references in this design, Choose Right Mouse Button  $\rightarrow$  Report  $\rightarrow$  Show References  $\rightarrow$  For Design.

A List of Unique References underneath the calc\_sot directory is displayed. An example reference item might be:

\$XILINX\_TUTORIAL/calc\_sot/alu/alu:mgc\_symbol[6]

This indicates that an ALU symbol (version 6 under Mentor Graphics' versioning system) is referenced by the path \$XILINX\_TUTORIAL/calc\_sot/alu/alu.

All references in the design should contain either \$LCA or \$XILINX\_TUTORIAL.

- 4. Close the List of Unique References window.

- 5. With the calc\_sot directory selected in the Navigator window, choose Right Mouse Button  $\rightarrow$  Edit  $\rightarrow$  Copy.

- 6. In the dialog box that appears, type the directory path where you want to copy the working copy of the tutorial files.

For example, to copy the files to /home/dum/tutor/mentor, enter the following:

/home/dum/tutor/mentor/calc\_sot

7. To keep the design references intact, select  $Options \rightarrow Convert$ References? No from the Copy dialog box.

Normally, you allow Design Manager to update design references when you copy a design directory. In this case, however, you should leave the \$XILINX\_TUTORIAL reference intact. To make sure the proper directory is referenced, modify the MGC\_LOCATION\_MAP accordingly after you copy the tutorial design.

- 8. Click **OK** to exit the Options dialog box.

- 9. Click **OK** again to exit the Copy dialog box and start the Copy process.

- 10. Use the Navigator to change directories to the location of the working copy of calc\_sot. (In the example above, you would click the four-arrow button at the bottom of the Navigator window, then type /home/dum/tutor/mentor/calc\_sot in the dialog box.)

- 11. Modify your MGC\_LOCATION\_MAP file so that the \$XILINX\_TUTORIAL variable points to the directory where the copy of calc\_sot is located. In the example above, change the \$XILINX\_TUTORIAL section of the file so that it reads:

\$XILINX\_TUTORIAL

/home/dum/tutor/mentor

- 12. Read the newly modified location map into Design Architect by selecting  $MGC \rightarrow Location Map \rightarrow Read Map$  from the menu bar.

- 13. In the dialog box that opens, type:

\$MGC\_LOCATION\_MAP

14. Click OK.

The \$XILINX\_TUTORIAL soft name now points to the new tutorial area.

# **Starting Design Architect**

To open the Calc design in Design Architect, perform the following steps:

- 1. Select MGC  $\rightarrow$  Location Map  $\rightarrow$  Set Working Directory from the menu bar. A small dialog box appears at the bottom of the screen.

- 2. Type **\$XILINX\_TUTORIAL/calc\_sot** in the Directory field of the dialog box, then select **OK** or press return. This sets the

working directory to the directory where you work on the tutorial.

- 3. Select the **\$XILINX\_TUTORIAL/calc\_sot/calc** design object in the Navigator window.

- 4. Select Right Mouse Button  $\rightarrow \texttt{Open} \rightarrow \texttt{pld}_da$ .

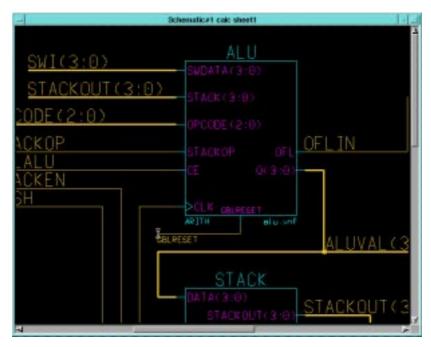

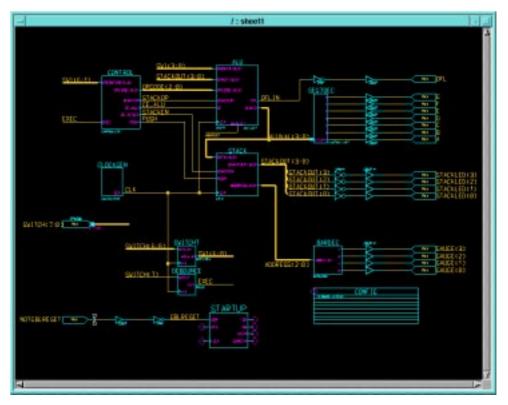

The Design Architect window appears and displays the Calc design as shown in the following figure.

Figure 11-2 Top-Level Schematic for Calc

5. Resize the Design Architect window to cover the entire screen.

# **Completing the Calc Design**

To complete the tutorial design, you need to link VHDL entities to symbols in the schematic using Vcom and Design Architect.

If you need to stop the tutorial at any time, be sure to save your work as follows:

1. Select  $Check \rightarrow Sheet$  from the menu bar.

A window appears containing the results of the design rule check.

2. After reviewing the contents of this window, close it and reselect the schematic window.

Warning: It is important to check your design first before saving it.

3. Select File  $\rightarrow$  save from the menu bar to save the design.

### **Design Description**

The Calc design is a four-bit processor with a stack. The processor performs functions between an internal register and either the top of the stack or data input from external switches. The results of the various operations are stored in the register and displayed in hexadecimal on a seven-segment display. The top value in the stack is displayed in binary on a bar LED. A count of the items in the stack is displayed as a "gauge" on another bar LED.

In this tutorial, you create a new symbol for the SEG7DEC component from its associated seg7dec.vhd description, then instantiate that symbol onto the Calc schematic. You then link an existing ALU symbol to its associated alu.vhd description. A CONFIG block and a STARTUP block have already been added to the Calc design as well. For more information on using CONFIG and STARTUP, see the "Schematic Design Tutorial".

The design consists of the following functional blocks:

- **ALU**—The arithmetic functions of the processor are performed in this block. This block is defined by the VHDL file alu.vhd.

- **CONTROL**—The opcodes are decoded into control lines for the stack and ALU in this module.

- **STACK**—The stack is a four-nibble storage device. It is implemented using synchronous RAM in the XC4000E design.

- **DEBOUNCE**—This circuit debounces the "execute" switch, providing a one-shot output.

- **SEG7DEC**—This block decodes the output of the ALU for display on the 7-segment decoder. You generate the symbol for this module from its behavioral VHDL description in seg7dec.vhd.

- **CLOCKGEN**—This block uses an internal oscillator circuit in XC4000E devices to generate the clock signal.

- **BARDEC**—This block shows how many items are on the stack on a "gauge" of four LEDs.

- **SWITCH7**—This is a user-defined module consisting of seven input flip-flops used to latch the switch data.

**Note:** Basic Xilinx design concepts such as assignment of pin properties, use of STARTUP and CONFIG, and incremental design methodology as well as details about Xilinx device architecture are not covered in this chapter. For more information on these topics, see the "Schematic Design Tutorial" chapter.

### Adding the SEG7DEC Component

On the Calc schematic, notice a space near the upper-right corner of the schematic between the ALUVAL(3:0) bus and the inputs to seven OBUF elements that feed LED outputs A through G. This is where the SEG7DEC symbol must be placed.

This component has a VHDL file, seg7dec.vhd, that describes its behavior. In this exercise, you compile the seg7dec.vhd file for simulation, generate a symbol for it, then instantiate the entity into the Calc schematic so that it may be simulated and built into the implemented device.

#### **Compiling the VHDL Entity**

To compile the VHDL file for SEG7DEC, follow these steps:

1. Take a look at the src/seg7dec.vhd file with the text editor you normally use.

This entity includes a case statement that decodes a four-bit number into a set of seven signals suitable for display on a sevensegment LED display. The src/seg7dec.vhd file is as follows:

```

process (Q)

begin

```

```

case Q is

when "0000" => DISPLAY <= "0000001";

when "0001" => DISPLAY <= "1001111";

when "0010" => DISPLAY <= "0010010";

when "0011" => DISPLAY <= "0000110";

when "0100" => DISPLAY <= "1001100";

when "0101" => DISPLAY <= "0100100";

when "0110" => DISPLAY <= "0100000";

when "0111" => DISPLAY <= "0001101";

when "1000" => DISPLAY <= "0000000";

when "1001" => DISPLAY <= "0000100";

when "1010" => DISPLAY <= "0001000";

when "1011" => DISPLAY <= "1100000";

when "1100" => DISPLAY <= "0110001";

when "1101" => DISPLAY <= "1000010";

when "1110" => DISPLAY <= "0110000";

when others => DISPLAY <= "0111000";

end case;

end process;

```

- 2. Close the src/seg7dec.vhd file.

- 3. To create a VHDL work library where compiled entities will reside, type the following at the system prompt from within the \$XILINX\_TUTORIAL/calc\_sot directory:

vlib mywork

A library directory called "mywork" now exists in the tutorial project directory.

4. Map this directory to "work" so that the VHDL compilation programs can recognize it:

vmap work mywork

You should now have a new file in your tutorial directory called modelsim.ini, which contains the following library entry:

```

[Library]

work = mywork

```

This allows the VHDL-simulation programs to recognize this as the working directory.

5. Compile the src/seg7dec.vhd file with the vcom command:

vcom -qspro\_syminfo src/seg7dec.vhd

The -qspro\_syminfo option tells VCOM to write out information needed by the Design Architect Symbol Generator.

- 6. With the Calc schematic still open in Design Architect, select  $Miscellaneous \rightarrow Generate$  Symbol from the menu bar.

- 7. In the Generate Symbol dialog box that appears, select Choose Source  $\rightarrow$  Entity.

The dialog box fields change as shown in the Generate Symbol dialog box in the following figure.

|                                           | rate Symbol                                                                           |

|-------------------------------------------|---------------------------------------------------------------------------------------|

| se Source Philist File Schem              | atic Intity                                                                           |

| ModelSim InitFile: jintor/cal             | Ic_soVinodelsim.ini Set list File                                                     |

| wy Logical Hame: Jwprk                    | Geose Library                                                                         |

| Entity Name: seg7dec                      | Choose Enlity                                                                         |

| alt Architecture: JorV, VHD               | archW, [ChdW]] Choese Arch                                                            |

| Pin Specing (in pin grids)                | Current Shape: box<br>Shape Arguments: [[2,2]                                         |

| Ves No<br>Replace existing?<br>Ves<br>Nes | Choose Shape<br>Activate symbol?<br>Ves<br>Activate symbol?<br>(Symbol must be saved) |

#### Figure 11-3 Generate Symbol Dialog Box

8. In the Generate Symbol dialog box, make sure the fields are set as shown in the following table:

| Field               | Value                                           |

|---------------------|-------------------------------------------------|

| QVHDL InitFIle      | \$XILINX_TUTORIAL/calc_sot/modelsim.ini         |

| Lib. Logical Name   | work                                            |

| Entity Name         | seg7dec                                         |

| Deflt. Architecture | "[ $"behavior$ ]", "HDL arch \", [ $''hdl$ "]]" |

| Place Comp. in Dir. | \$XILINX_TUTORIAL/calc_sot                      |

| Pin Spacing         | 2                                               |

| Shape Arguments     | [2,2]                                           |

| Sort Pins?          | Yes                                             |

| Replace existing?   | No                                              |

| Activate symbol?    | No                                              |

Table 11-2 Generate Symbol Settings for SEG7DEC

**Note:** You can select the architecture setting from a list by click on the **Choose Arch** button. Since only one architecture has been compiled for the SEG7DEC entity, you may also leave this field blank.

9. Click OK.

After a few moments, the Symbol Editor appears with the newly created SEG7DEC component. Note the properties attached to this symbol and its pins. These properties allow the underlying entity and the upper-level schematic portion to be simulated concurrently in QuickSim Pro.

**Note:** If you get the error "Entity source work\_library/\_parsed.vhd does not exist," make sure you specified the -qspro\_syminfo option on the VCOM command line.

10. Add "SEG7DEC" text to the symbol as shown. (If you do not know the procedure for this, refer to the instructions in the "Schematic Design Tutorial".)

Figure 11-4 Generated SEG7DEC Symbol

All symbols that have an associated non-schematic model must have a FILE property attached to them so that the Xilinx netlister (NGDBUILD) can incorporate these portions of the design into the implemented design. The value of this property is the actual filename of the submodule netlist. This filename can have one of several different extensions, based on the netlist format it uses.

Table 11-3 Common FILE Property Extensions

| Extension | Netlist Format                          |  |  |

|-----------|-----------------------------------------|--|--|

| .edif     | Generic Xilinx-compatible EDIF 2.0      |  |  |

| .xnf      | Generic XNF (Xilinx Netlist Format) 6.x |  |  |

| .sedif    | Synopsys Xilinx-compatible EDIF 2.0     |  |  |

| .sxnf     | Synopsys XNF 6.x                        |  |  |

The presynthesized SEG7DEC module included with this tutorial was generated by Synopsys' Design Compiler, which uses SEDIF.

11. Select the body of the SEG7DEC symbol and add the following property:

Name: FILE Value: seg7dec.sedif

12. Check and Save the symbol.

Now that a symbol exists for this component, you can instantiate it onto the top-level Calc schematic.

- 13. With the Calc schematic window active, click CHOOSE SYMBOL from the Schematic Palette and select the seg7dec component.

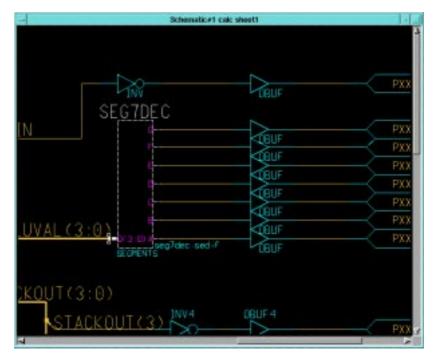

- 14. Instantiate this component between the ALUVAL(3:0) bus and the nets that lead to the outputs A-F as shown below.

Figure 11-5 Adding the SEG7DEC Symbol

- 15. Add the instance name **SEGMENTS** to the SEG7DEC symbol. (Add property **INST**, value **SEGMENTS**.)

- 16. Check and Save the Calc schematic. Leave the schematic open.

### Linking a VHDL Entity to the ALU Component

VHDL can also be associated with a pre-existing symbol. The following procedure links the alu.vhd entity with the ALU symbol, which has already been instantiated on the Calc schematic.

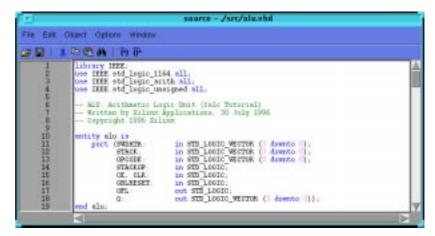

As with SEG7DEC, ALU has a VHDL file, alu.vhd, that describes its behavior. In this exercise, you compile the alu.vhd file for simulation, link the compiled model to the existing ALU symbol, then update the instantiated entity in the Calc schematic so that it may be simulated and built into the implemented device.

### **Compiling the VHDL Entity**

To compile the VHDL file for ALU, follow these steps.

1. Take a look at the alu or seg7dec.vhd file with the text editor you normally use.

This entity includes a four-bit data register, several multi-bit gate functions (AND, OR, and XOR), and an adder-subtractor. To model the device's system-wide global set/reset, an additional port, GBLRESET, has been added from the schematic-based ALU design. (See the "Schematic Design Tutorial".) This signal is brought into the process block that controls the four-bit data register:

#### VHDL ALU Register Description:

```

process (CLK, GBLRESET)

begin

if (GBLRESET='1') then

QIN <= "0000";

OFL <= '0';

elsif (CLK'event and CLK='1') then

if (CE='1') then

if (QRESET='1') then

OIN <= "0000";

OFL <= '0';

else

OIN <= MUX;

OFL <= OVER;

end if;

end if;

end if;

end process;

```

The GBLRESET signal is written as an explicit asynchronous clear. This allows you to connect the registers in the ALU entity to the system-wide global-set/reset signal from the schematic. In an all-schematic design, the system-wide global-set/reset net does not need to be connected, since it is implicitly connected to all flip-flops in a device, both for simulation and implementation. For simulation purposes, however, this signal needs to be explicitly connected to all flip-flops in all VHDL modules. The Xilinx Core Tools recognize this as a redundant connection and subsequently trim it out of the implemented design.

2. When you are finished perusing the ALU VHDL description, close the file.

Since a work directory already exists for compiling VHDL modules, you can go directly to compiling the ALU entity.

3. Compile the src/alu.vhd file with the VCOM command:

```

vcom -explicit -qspro_syminfo src/alu.vhd

```

The "-explicit" option allows VCOM to tolerate multiply-defined standard functions. This is required because the equality operator ("=") is defined in both the ieee.std\_logic\_1164 and ieee.std\_logic\_unsigned packages, both of which are called out in

ieee.std\_logic\_unsigned packages, both of which are called out in the alu.vhd file.

- 4. With the Calc schematic still open in Design Architect, select the ALU symbol.

- 5. Open down into the symbol by selecting Right Mouse Button  $\rightarrow$  Open Down.

- 6. Select symbol:alu.

- 7. Click OK.

The Symbol Editor appears.

If you performed the Schematic Design Tutorial with the all-schematic-based Calc design, you should notice that the ALU symbol has an extra pin, GBLRESET, that corresponds to the extra VHDL port mentioned above.

8. From the menu bar, select  $\mathtt{File} \to \mathtt{Import \ VHDL \ Entity}.$

The Import VHDL Entity dialog box appears.

|                       | Import Entity Info              |                |

|-----------------------|---------------------------------|----------------|

| ModelSim InitFile:    | ntor/calc_sot/modelsim.ini      | Set Init File  |

| ibrary Logical Name:  | work                            | Choose Library |

| Entity Name:          | alu                             | Choose Entity  |

| )efault Architecture: | or\", \"HDL arch\", [\"hdl\"]]" | Choose Arch    |

#### Figure 11-6 Import VHDL Entity Dialog Box

9. Set the following values in the dialog box:

Table 11-4 Import VHDL Entity Settings for ALU

| Field               | Value                                    |

|---------------------|------------------------------------------|

| QVHDL InitFIle      | \$XILINX_TUTORIAL/calc_sot/modelsim.ini  |

| Lib. Logical Name   | work                                     |

| Entity Name         | alu                                      |

| Deflt. Architecture | "[\"behavior\",\"HDL arch\", [\"hdl\"]]" |

**Note:** You can select the architecture setting from a list by clicking on the **Choose Arch** button. Since only one architecture has been compiled for the ALU entity, you may also leave this field blank.

10. Click ok.

In the Symbol Editor, the ALU symbol's body and pins are annotated with properties similar to those that Generate Symbol attached to the SEG7DEC symbol. These properties allow the underlying entity and the upper-level schematic portion to be simulated concurrently in QuickSim Pro. **Note:** If you get the error "Entity source *work\_library/\_*parsed.vhd does not exist," make sure you specified the -qspro\_syminfo option on the VCOM command line.

Figure 11-7 ALU Symbol with VHDL-Import Properties

Since the ALU module is also a non-schematic element, you must attach a FILE property to it so the Xilinx netlister (NGDBUILD) can incorporate this portion of the design into the implemented netlist. The ALU netlist included with this tutorial was synthesized by Exemplar's Galileo, and thus uses generic XNF.

11. Select the body of the ALU symbol and add the following property:

Name: FILE Value: alu.xnf

12. Check and Save the symbol.

Since the symbol has now changed, you must reflect the change in the top-level Calc schematic.

13. With the Calc schematic window active, select the ALU symbol, then select Right Mouse Button  $\rightarrow$  Update  $\rightarrow$  Auto.

This updates the ALU instantiation with the new symbol properties.

The GBLRESET pin on the ALU symbol must be attached to the global set/reset signal from the top-level design. This signal is the one connected to the GSR input on the STARTUP block. In the case of Calc, this net is also called GBLRESET.

14. Attach a new net to the GBLRESET pin and name it GBLRESET.

Figure 11-8 Updating the ALU Symbol

- 15. Check and Save the Calc schematic.

- 16. Exit Design Architect.

# Using a Constraints File

Using a constraints file, you can supply constraints information in a textual form. An example of a constraints file is shown below. The

example shows the user constraints file, calc\_4ke.ucf, that is supplied with this tutorial. The constraints file syntax is the same for all device families.

**Note:** You may also place location constraints directly on the schematic. For more information, see the "Schematic Design Tutorial" chapter.

The place and route software must be instructed to read and apply the .ucf file when the design is read into the Xilinx Design Manager. The procedure for doing this is detailed later in the "Using the Xilinx Design Manager".

**Example Constraints File:**

```

# CALC_4KE.UCF

# User constraints file for CALC, XC4003E-PC84

# Uses angle brackets, as per PLD_MEN2EDIF option

NET SWITCH<7>

LOC=P19;

NET SWITCH<6>

LOC=P20;

NET SWITCH<5>

LOC=P23;

NET SWITCH<4>

LOC=P24;

NET SWITCH<3>

LOC=P25;

NET SWITCH<2>

LOC=P26;

NET SWITCH<1>

LOC=P27;

NET SWITCH<0>

LOC=P28;

NET A

LOC=P49;

NET B

LOC=P48;

NET C

LOC=P47;

NET D

LOC=P46;

NET E

LOC=P45;

NET F

LOC=P50;

NET G

LOC=P51;

NET OFL

LOC=P41;

NET GAUGE<3>

LOC=P61;

NET GAUGE<2>

LOC=P62;

NET GAUGE<1>

LOC=P65;

NET GAUGE<0>

LOC=P66;

NET STACKLED<3>

LOC=P57;

NET STACKLED<2>

LOC=P58;

NET STACKLED<1>

LOC=P59;

NET STACKLED<0> LOC=P60;

```

NET NOTGBLRESET LOC=P56;

# **Performing Functional Simulation**

Functional simulation is performed before design implementation to verify that the schematic that you have designed is logically correct. All components in the Calc design have built-in simulation models so little pre-processing is necessary. However, every top-level schematic design in Mentor Graphics must have a simulation viewpoint before you can simulate it in QuickSim Pro. The viewpoint describes how a design should be interpreted, including what components in the design are primitives, as well as how components within the design hierarchy should be modeled.

**Note:** The following instructions refer to two related but different programs: ModelSim and QuickSim Pro. ModelSim is Mentor Graphics' HDL-only simulator, while QuickSim Pro is a co-simulation tool that runs both ModelSim to simulate the HDL portions of a design and QuickSim to simulate the schematic portions. QuickSim Pro runs a process known as a FlexSim backplane through which the two "solvers" (ModelSim and QuickSim) communicate with each other.

Also note that the instructions that follow do not have detailed information on basic QuickSim operations such as selecting nets and displaying Trace and List windows. For information on these procedures, please refer to the "Schematic Design Tutorial".

### Using Pld\_dve

To use the PLD Design Viewpoint Editor to generate a design viewpoint to tell QuickSim (as run by QuickSim Pro) how to interpret certain Xilinx-specific design properties, follow these steps.

- 1. Select the calc design object from the appropriate directory in the Navigator window.

- 2. Invoke pld\_dve on the design by selecting Right Mouse Button  $\rightarrow$  Open  $\rightarrow$  pld\_dve.

A dialog box appears. Note that the component name, Calc, is entered automatically with a fully qualified path.

| Component Name //home/clum/butor/calc_sot/calc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Navigator |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Select One: Simulation Custom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

| Vewpoint Name: default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

| PLD Technology:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| XC2000A<br>XC2000A<br>XC2100A<br>XC2100E<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC4000EX<br>XC400EX<br>XC400EX<br>XC400EX<br>XC400EX<br>XC400EX<br>XC400EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX<br>XC40EX |           |

| Invoke stand alone dve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

| OK Reset Cancel HE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1P        |

Figure 11-9 Invoking Pld\_dve for Functional Simulation

- 3. Select the XC4000E PLD Technology from the listing as shown in the figure above. (Leave other options set to their defaults, as shown in the figure.)

- 4. Click OK.

The pld\_dve script executes.

5. Once pld\_dve completes, dismiss the shell window in which it executed.

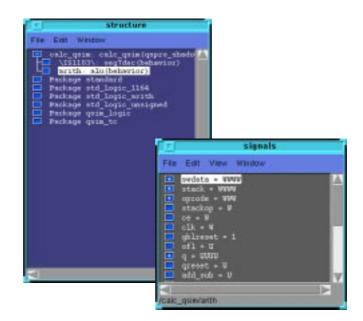

# Invoking QuickSim Pro

To invoke QuickSim Pro for functional simulation on the Calc design, follow these steps:

- 1. Select the Calc design object in the Navigator window.

- 2. Invoke QuickSim Pro on the design by selecting Right Mouse Button  $\rightarrow$  Open  $\rightarrow$  QSPro.

A dialog box appears. Note that the component name, Calc, is entered automatically with a fully qualified path. 3. Since the top-level Calc design is a schematic (EDDM model), verify that EDDM Design is the design set to Invoke on.

|                           | Qui               | ckSim Pro             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|-------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| evoke on EDDM Design      | EMBDY             | Configuration         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Pathname //home/dum/t     | utor/calc_sot/ca  | alc                   | Navagator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                           |                   |                       | And the second s |

| Symbol                    | Intentice         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NOTE: You may set op      | tions from any o  | f the following cate  | gories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OPTIONS category:         | Gapra H           | OL GLICKSHII          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Netlister exteriorito     | 400.00            |                       | Navigator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                           | Carlo Paranessor  |                       | ALC: CONTRACTOR OF CONTRACTOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |